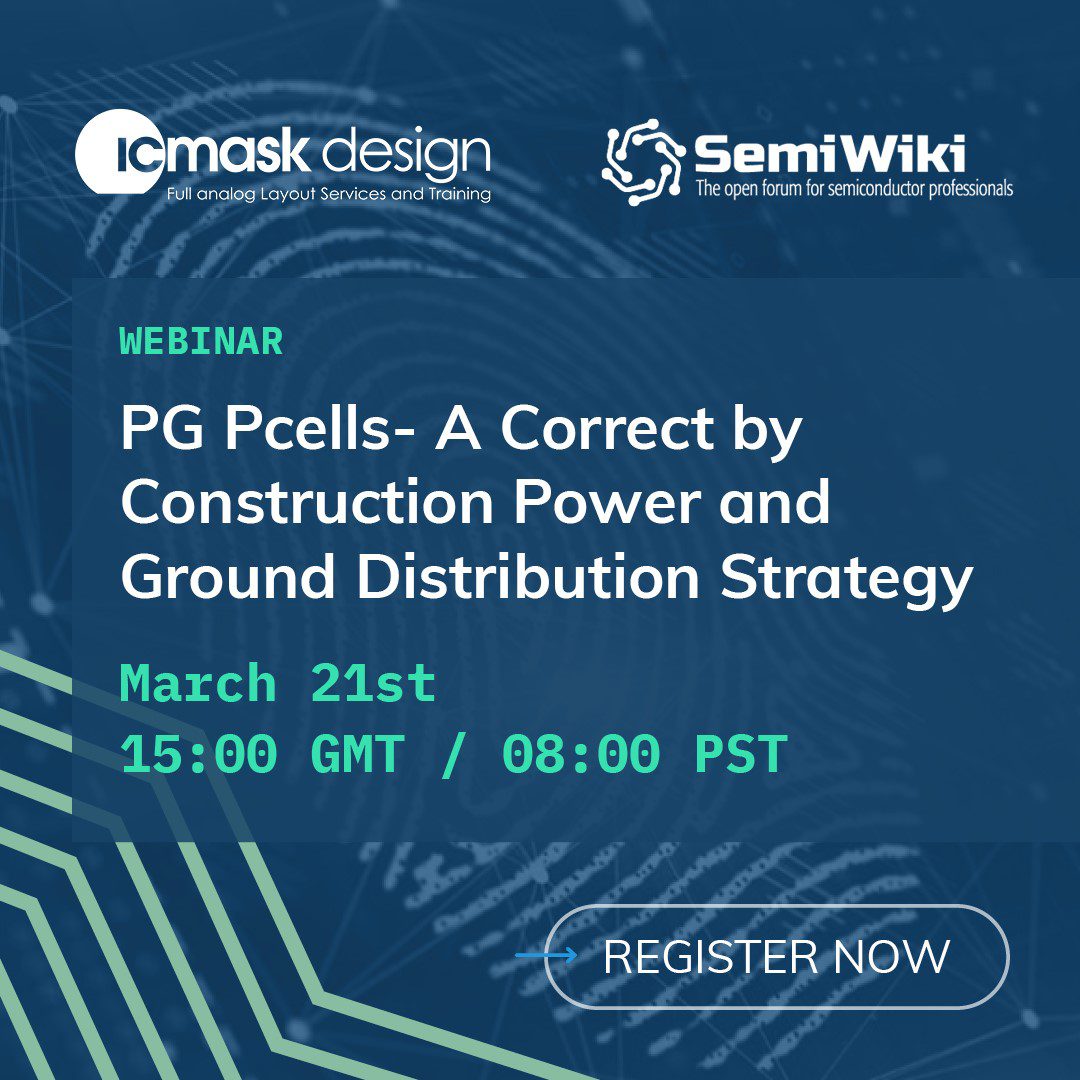

PG Pcells- A Correct by Construction Power and Ground Distribution Strategy

Proper Power Strategy for Layouts comes with several requisites that pose great difficulty and are hard to balance without compromising on one or more aspects. Power strategy adds difficulty to an already complex process of floor-planning and is a time and labour intensive implementation. It poses many challenges like hard to meet EM/IR specifications for a design, integration of different gate lengths in the same circuit, managing noise coupling from power/ground to signals while simultaneously maintaining BEOL density at different levels of hierarchy macro, IP, or chip. Our approach to PG Pcells acts as a facilitator to floor-planning by providing an initial structure. It improves Layout efficiency and accuracy by replacing numerous flat metals and vias with few instances or mosaics which in turn reduces dependence upon frequent EM&IR runs as robust EM&IR considerations for both power/ground and the signal from get-go reduces the chances of EM&IR failures.

Speaker Bio:

IC Mask Design Engineer Fabio Commodi is a former Photolithography Process Engineer and a current Layout Design Engineer with over 5 years’ experience in the physical implementation of Analog, RF, & Mixed-signal integrated circuits. Fabio has been involved in many projects ranging across a number of foundries and nodes contributing at the block to the top-level.

*This webinar is in partnership with SemiWiki and IC Mask

REGISTER HERE >

Share this on...